鐵電晶體管(FeFET)具有非易失性數據存儲、納秒級的編程/擦除速度、低功耗操作、超長的數據保存時間以及與CMOS工藝兼容等優點,被認為是未來非易失存儲器應用的候選器件。在5nm技術節點以下,由于器件柵長(小于18納米)和鐵電薄膜厚度(大約10納米)相近,基于FinFET和水平環柵晶體管(GAAFET)的FeFET無法進一步微縮,而垂直環柵晶體管(VGAAFET)不受柵長的約束,同時在3D集成和布線上有明顯優勢,具有大幅增加集成度的潛力,因此更適合5納米技術節點以下的FeFET結構。

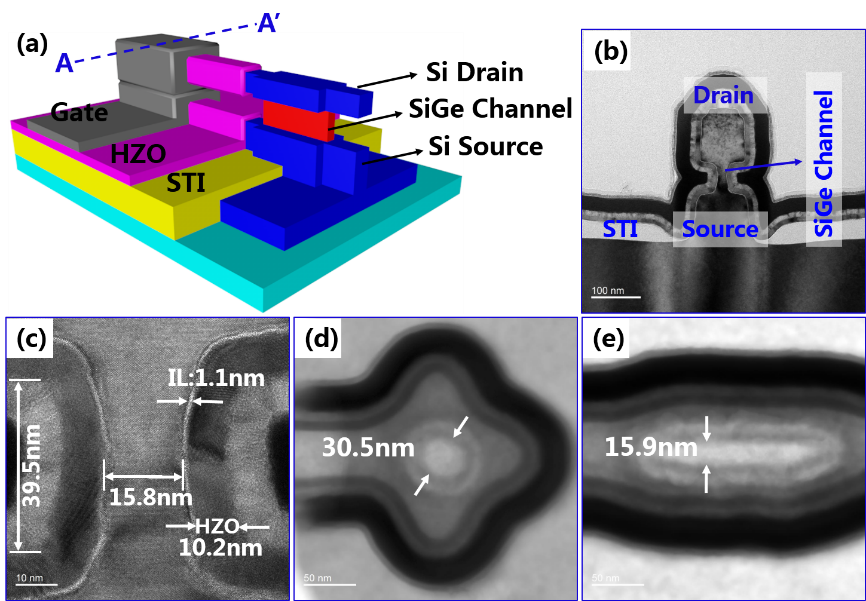

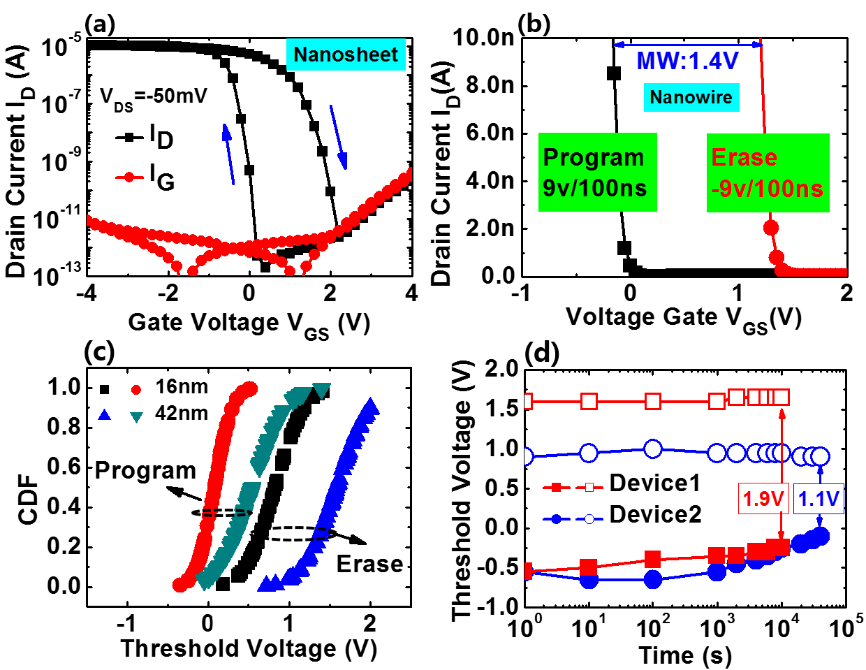

微電子所集成電路先導工藝研發中心朱慧瓏研究員團隊利用自主研發的集成工藝,制造出了具有自對準柵極的鐵電垂直環柵納米晶體管(Fe-VSAFET),其中包括柵長為40納米,溝道厚度為16納米的納米片和直徑為30納米的納米線兩類器件。該器件具有小于pA級的漏電,大于107的開關比,100ns級的編程/擦除速度,和2.3V的最大存儲窗口等優異的電學特性,并且制程工藝與主流CMOS兼容。該成果近日以“Ferroelectric Vertical Gate-All-Around Field-Effect-Transistors with High Speed, High Density, and Large Memory Window”為題發表在《IEEE Electron Device Letters》上(DOI: 10.1109/LED.2021.3126771)。微電子所博士生黃偉興為該文第一作者,朱慧瓏研究員、張永奎高級工程師為該文通訊作者。

該成果得到中科院戰略先導專項預研項目和微電子所所長基金項目資助。

論文鏈接:https://ieeexplore.ieee.org/document/9611160

圖1.(a)Fe-VSAFET器件結構圖,(b)-(e)Fe-VSAFET的TEM頂視和截面圖

圖2.(a)Fe-VSAFET直流電壓掃描測試,(b)Fe-VSAFET脈沖編程/擦除特性測試,(c)Fe-VSAFET脈沖編程/擦除閾值電壓累積分布函數,(d)Fe-VSAFET保留時間測試

綜合信息