近日,2020國際電子器件大會(IEDM)以視頻會議的形式召開。會上,微電子所劉明院士科研團隊展示了阻變存儲器芯片集成領域的最新研究成果。

阻變存儲器(RRAM)因其CMOS工藝兼容性好、微縮能力強、可靠性高等優勢,被認為是先進工藝節點上取代e-flash的有力候選者。但其能否集成在10納米邏輯工藝平臺是影響RRAM未來市場的關鍵因素。

劉明院士團隊首次在14納米 FinFET邏輯工藝平臺上開展了RRAM的集成工作,實現了1Mbit的嵌入式RRAM存儲芯片,1T1R單元面積為0.022um2,芯片存儲密度為13.4Mb/mm2,居世界前列。針對RRAM器件與邏輯單元之間的不兼容性,團隊提出了負電壓偏置的編程方案,通過在芯片中引入深N阱工藝,使陣列可以施加負電壓以降低施加電壓的絕對值進而減小傳輸路徑上的高壓風險。團隊采用位線轉置的優化陣列架構,降低了晶體管的擊穿風險。團隊發現操作電壓、編程電流和后端RC是影響微縮的重要因素,進而提出了RRAM在10納米及以下節點集成的建議設計規則,并采用1T2R的陣列架構提高存儲密度。該工作對提升RRAM在先進工藝節點下的嵌入式應用具有一定的指導意義。

基于上述研究成果的論文“First Demonstration of OxRRAM Integration on 14nm FinFet Platform and Scaling Potential Analysis towards Sub-10nm Node”入選2020 IEDM。微電子所許曉欣副研究員為論文第一作者。

圖1 (a)14nm FinFET平臺開發的RRAM結構示意圖。b)RRAM單元的TEM橫截面圖像。(c)2Finger 結構的邏輯器件。(d)RRAM的疊層結構

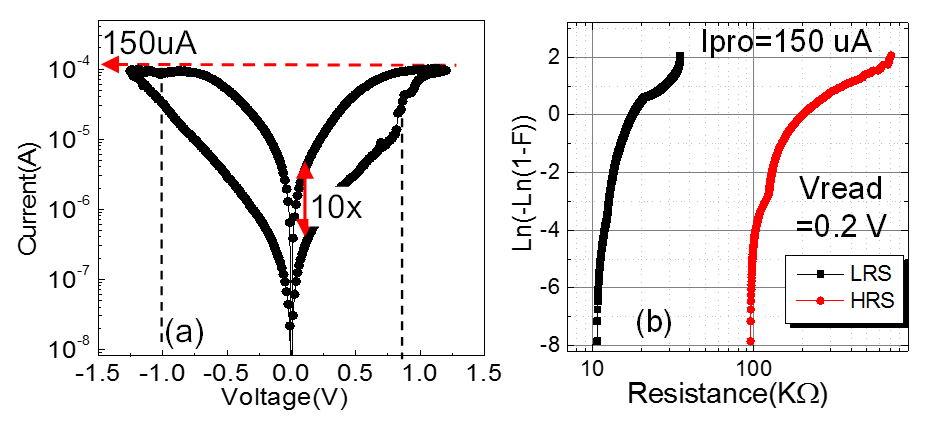

圖2 RRAM單元的基本電學特性。(a)IV特性曲線;(b)4Kb存儲陣列中高低阻態分布

綜合信息